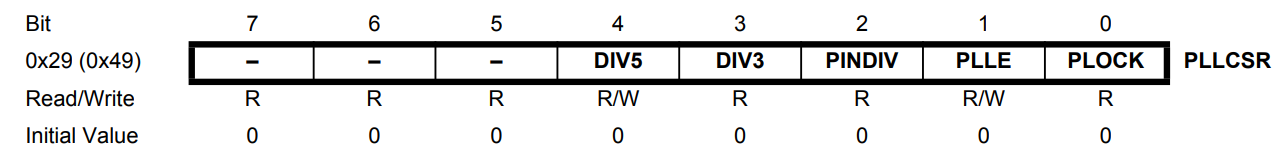

There seems to be an error in the datasheet for ATmega32U2 (and possibly also ATmega8U2 and ATmega16U2). There, the bits of the PLLCSR register are named DIV5, DIV3, PINDIV, PLLE and PLOCK.

However, it seems in iom32uh.h the prescaler bits are called PLLP0, PLLP1 and PLLP2 respectively. Therefore, these are the correct C statements to start the PLL:

- For an 8Mhz external clock

PLLCSR = ((0<<PLLP2) | (0<<PLLP1) | (0<<PLLP0) | (1<<PLLE)); - For a 16Mhz external clock

PLLCSR = ((0<<PLLP2) | (0<<PLLP1) | (1<<PLLP0) | (1<<PLLE));

Hope that saved you some time and digging.

I am a freelance IT consultant, software developer and commercial pilot from Vienna, Austria.

I am a freelance IT consultant, software developer and commercial pilot from Vienna, Austria.